# INTERNATIONAL JOURNAL OF ENGINEERING SCIENCES & RESEARCH TECHNOLOGY

# Reduction of Total Harmonic Distortion Using Filtered SVPWM in Multiphase Voltage Source Inverters

# P.Raghuram<sup>\*1</sup>, P.Sadanandam<sup>2</sup>, P.Nagarjuna Reddy<sup>3</sup>

\*1,2 Department of Electrical and electronics Engineering, Vaagdevi College Of Engineering, JNT University, Hyderabad, Andhra Pradesh, India

<sup>3</sup> Department of Electrical and electronics Engineering, Kakatiya Institute of Technology and Science,

Kakatiya University, Warangal, Andhra Pradesh, India

puranam.raghuram@gmail.com

# Abstract

In recent years, multiphase PWMs have been proposed because of their increased efficiency, reduced torque pulsation, improved fault tolerance, and lower power handling requirement by adopting multiphase machines. In the digital implementation, multiphase reference voltages are sampled and fed into the digital modulator to produce gating signals at a constant clock rate f. This means a finite pulse-width resolution because the gating state transition can only occur at some specific time instants depending on f. This will result in a deviation of produced phase voltages from the desired phase voltages, i.e., increasing harmonic distortion especially for a small modulation index signal.

In the present paper a filtered space-vector pulse-width modulation (SVPWM) considering finite pulsewidth resolution is proposed to produce a switching sequence with reduced baseband harmonics for multiphase voltage source inverters (VSI). This is achieved by incorporating a pseudo feedback loop regarding weighted voltage difference between desired and produced phase voltages.

# Keywords: SVPWM, Voltage Source inverters, Harmonic Distortion.

### Introduction

PWM inverters are quite popular in industrial applications. PWM techniques are characterized by constant amplitude pulses. The width of these pulses is however modulated to obtain inverter output voltage control and to reduce its harmonic content. The different PWM techniques are as under:

- (a) Single-pulse modulation

- (b) Multiple pulse modulation

- (c) Sinusoidal pulse width modulation (Carrier

- based Pulse Width Modulation Technique)

Various pulse-width modulations (PWM) such as third harmonic injection PWM, zero-sequence injection PWM, space-vector PWM (SVPWM), and unified PWM have been proposed to generate the control commands of three-phase voltage source inverter (VSI) for ac variable speed drives. In recent years, multiphase PWMs have been proposed because of their increased efficiency, reduced torque pulsation, improved fault tolerance, and lower power handling requirement by adopting multiphase machines.

In the digital implementation, multiphase reference voltages are sampled and fed into the digital modulator to produce gating signals at a

constant clock rate f. This means a finite pulse-width resolution because the gating state transition can only occur at some specific time instants depending on f. This will result in a deviation of produced phase voltages from the desired phase voltages, i.e., increasing harmonic distortion especially for a small modulation index signal. For example, when system master clock frequency and reference sampling frequency are given as 48 and 3 kHz, respectively, the maximum refreshing rate of gating signals is f =48 kHz and the pulse-width resolution is 4-bit within each input period ( $48k = 3k \times 24$ ). Thus, the worstcase rounding error for the duty ratio is 1/32 =0.03125. For small modulation index, the effect of error on signal distortion becomes quite significant. Further, if a 16-bit pulse-width resolution is desired, the master clock needed is 196.61MHz for 3 kHz reference sampling frequency and is about 1.31 GHz for ultrasonic carrier. This will increase the cost and power consumption of the devices.

To alleviate the adverse effect induced by finite pulse-width resolution, proposals were reported to achieve higher precision of duty ratios without increasing clock rate. In, a single-phase PWM to regulate a dc voltage command was proposed by

using an error accumulator and lookup tables. A feedback quantization scheme proposed for threephase VSI spreads the spectrum of the produced phase currents/voltages in a wide frequency band. The general solution using SVPWM for multiphase VSIs was reported. The multiphase SVPWM was formulated as a matching problem between the reference and the switching waveform without considering the finite pulse-width resolution.

In this study, the frequency-weighted error due to finite resolution is considered in the objective function to emphasize the quality of in-band signal matching. The frequency weighting is realized by filtering the error signals. This results in a multipleinput–multiple-output (MIMO) pseudo feedback architecture. Based on similar analysis, the block diagram for VSI systems of any phase number can be obtained.

# Multiphase VSI Filtered SVPWM with Feedback

A. Multiphase Voltage Source Inverter:

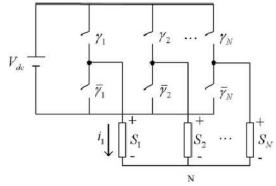

Fig. 1 depicts the simplified structure of an N-phase VSI where  $S_1, S_2, \ldots, SN$  are the output phase voltages of the inverter (with reference to the neutral point). Two switching states exist in one phase leg: only the upper or the lower switch is turned ON. The switching state is denoted as +1 (0) when the upper (lower) switch of the phase leg is turned ON. Then, the gating states can be represented by a vector  $\mathbf{s} = [s_1 \ s_2 \ \cdots \ s_N]^T$  where  $s_1, s_2, \ldots, s_N \in$  $\{0,1\}$  are the states of phase legs. Equation (1) gives the relationship between phase voltage vector,  $S = [S_1$  $S_2 \cdots S_N$ <sup>T</sup>, and the gating state. Notably, for an Nphase VSI, 2N gating states exist and each corresponds to a different phase voltage vector (also called a space vector) except for two zero switching states,  $s = [0 \cdots 0]T$  and  $s = [1 \cdots 1]^T$

$$\mathbf{S} = \begin{bmatrix} S_1 \\ S_2 \\ \vdots \\ S_N \end{bmatrix} = \begin{bmatrix} (N-1)/N & -1/N & \cdots & -1/N \\ -1/N & (N-1)/N & \ddots & \vdots \\ \vdots & \ddots & \ddots & -1/N \\ -1/N & \cdots & -1/N & (N-1)/N \end{bmatrix} \times \begin{bmatrix} s_1 \\ s_2 \\ \vdots \\ s_N \end{bmatrix} \triangleq \mathbf{S}_c \mathbf{s}$$

(1)

Remark 1: Multiplying  $[1 \cdots 1]$  on both sides of (1), we obtain that the phase voltage vector produced by the N-phase VSI (for the y-connected load) must satisfy  $\sum_{j=1}^{N} S_j = 0$ .

**B. Signal Matching Objective:**

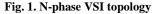

Fig.2. Model circuit of a winding of a motor

Given a desired phase voltage **r**, the objective of the modulator is to produce gating signals for VSI to recover the desired phase voltages on load windings. However, the phase voltages produced are restricted. For example, only seven different phase voltages can be produced by a three-phase VSI. Therefore, it is necessary to consider the characteristics of the load. The load is usually approximated by a serial-connected resistance and inductance circuit (refer to Fig. 2). The phase current is expressed by passing the produced phase voltage through a low-pass filter

$$P = \begin{cases} \begin{bmatrix} 0\\0\\0 \end{bmatrix}, \begin{bmatrix} 2/3\\-1/3\\-1/3 \end{bmatrix}, \begin{bmatrix} -1/3\\2/3\\-1/3 \end{bmatrix}, \begin{bmatrix} -1/3\\-1/3\\2/3 \end{bmatrix}, \begin{bmatrix} -2/3\\1/3\\1/3 \end{bmatrix}, \\ \begin{bmatrix} 1/3\\-2/3\\1/3 \end{bmatrix}, \begin{bmatrix} 1/3\\1/3\\-2/3 \end{bmatrix}, \begin{bmatrix} 1/3\\1/3\\-2/3 \end{bmatrix} \end{cases}$$

$$i_{1} = \frac{1}{sL+R}S_{1}$$

(2)

For an *N*-phase sinusoidal reference input **r** with phase shift  $2\pi/N$ , it is intuitive that the desired phase currents are also *N*-phase sinusoidal waves. Therefore, the objective is to find the switching states (gating states) such that the produced phase voltages are sinusoidal waves after low-pass filtering or alternatively, the difference between desired and produced phase voltages within low frequency band shall be minimized.

#### **C. Problem Formulation:**

The *N*-dimensional desired phase voltage vector satisfying (3) can be written in the form  $\mathbf{r} = [S_1^* S_2^* \cdots S_N^*]^T$  where

$$S_1^* + S_2^* + \dots + S_N^* = 0 \tag{3}$$

Assume that the controller input sampling frequency is  $f_c$  and that the pulse-width resolution within each

input period is b bits, i.e., the controller outputs are updated at a rate  $2^b \times f_c$  Hz. The average phase voltage produced on the windings within one input period is

$$\bar{\mathbf{v}}(k) = \frac{1}{2^{h}} \sum_{j=0}^{2^{\nu}-1} \mathbf{v}(j) = \frac{1}{2^{h}} \sum_{j=0}^{2^{t}-1} \mathbf{S}_{c} \mathbf{s}(j)$$

(4)

Where  $\mathbf{v}$  (*j*), one of the space vectors, is the corresponding phase voltage vector induced by the *j*th selected gating state s(j) within one input period. Note that the image of  $\bar{v}$  is all possible linear combinations of  $2^b$  basic vectors. The objective of the proposed modulator is to determine gating states (or  $\mathbf{v}$  (*j*)) that minimize filtered error power within each input period. The filtered error is represented as

$$\mathbf{E}(\mathbf{z}) = \mathbf{W}(z) \left( \mathbf{R}(z) - \bar{\mathbf{V}}(z) \right)$$

<sup>(5)</sup>

Where W(z) is an  $N \times N$  filter matrix and R(z),  $\overline{v}(z)$  are z-transform of the elements in r,  $\overline{v}$ , respectively. A pth-order low pass filter, denoted as w (z), is selected as the weighting filter for each phase to enhance low-frequency-band performance, i.e., W(z) is a diagonal matrix with w(z), a singleinput-single output (SISO) transfer function, on its diagonal terms. w(z) can be represented in the statespace form as

$$w(z) = d + c (z\mathbf{I} - \mathbf{a})^{-1} \mathbf{b}$$

(6)

(6)

(6)

Where a  $\in \mathbb{R}^{p \times p}$ , b  $\in \mathbb{R}^p$ , c  $\in \mathbb{R}^{1/2}$ Further, the state-space form of W(z) is

$$\mathbf{x} (k+1) = \mathbf{A} \mathbf{x} (k) + \mathbf{B} (\mathbf{r} (k) - \bar{\mathbf{v}} (k))$$

$$\mathbf{e} (k) = \mathbf{C} \mathbf{x} (k) + \mathbf{D} (\mathbf{r} (k) - \bar{\mathbf{v}} (k))$$

(7)

Where e (*k*)  $\in RN$  is the filtered error vector and **x** (*k*)  $\in \mathbb{R}^{pN}$  is a system state vector. Then, (A,B,C,D) can be written as

$$\mathbf{A} - \begin{bmatrix} \mathbf{a} & \mathbf{0}_{a} & \cdots & \mathbf{0}_{a} \\ \mathbf{0}_{a} & \mathbf{a} & \ddots & \vdots \\ \vdots & \ddots & \ddots & \mathbf{0}_{a} \\ \mathbf{0}_{a} & \cdots & \mathbf{0}_{a} & \mathbf{a} \end{bmatrix}, \quad \mathbf{B} - \begin{bmatrix} \mathbf{b} & \mathbf{0}_{b} & \cdots & \mathbf{0}_{b} \\ \mathbf{0}_{b} & \mathbf{b} & \ddots & \vdots \\ \vdots & \ddots & \ddots & \mathbf{0}_{b} \\ \mathbf{0}_{b} & \cdots & \mathbf{0}_{b} & \mathbf{b} \end{bmatrix}$$

$$\mathbf{C} = \begin{bmatrix} \mathbf{c} & \mathbf{0}_{c} & \cdots & \mathbf{0}_{c} \\ \mathbf{0}_{c} & \mathbf{c} & \ddots & \vdots \\ \vdots & \ddots & \ddots & \mathbf{0}_{c} \\ \mathbf{0}_{c} & \cdots & \mathbf{0}_{c} & \mathbf{c} \end{bmatrix}, \text{ and } \mathbf{D} = \begin{bmatrix} d & \mathbf{0} & \cdots & \mathbf{0} \\ 0 & d & \ddots & \vdots \\ \vdots & \ddots & \ddots & \mathbf{0} \\ \mathbf{0} & \cdots & \mathbf{0} & d \end{bmatrix}$$

Where  $\mathbf{0}_{a}$ ,  $\mathbf{0}_{b}$ , and  $\mathbf{0}_{c}$  are the zero matrices with dimensions  $\mathbf{0}_a \in \mathbb{R}^{p \times p}$ ,  $\mathbf{0}_b \in \mathbb{R}^p$ , and  $\mathbf{0}_c \in \mathbb{R}^{1 \times p}$ . The signal matching problem becomes

$$\min_{\mathbf{v}(j) \in \text{basic vectors}} \|\mathbf{e}(k)\|_2^2 = \min_{\mathbf{v}(j) \in \text{basic vectors}}$$

$$\|\mathbf{C}\mathbf{x}(k) + \mathbf{D}\mathbf{r}(k) - \mathbf{D}\bar{\mathbf{v}}(k)\|_{2}^{2}$$

(9)

$$\mathbf{\bar{v}}(k) = \frac{1}{2^{b}} \sum_{j=0}^{2^{b}-1} \mathbf{S}_{c} \mathbf{s}(j)$$

# **D. Solution of the Minimization Problem:**

The solution to (9) is split into three parts: 1) Finding a feasible and optimal  $\bar{v}(k)$ , denoted as  $\mathbf{v}^*(k)$ , such that power of filtered error is minimized; 2) solving the matching problem

$\bar{v}(k) = \frac{1}{2^b} \sum_{j=0}^{2^b - 1} \mathbf{S}_c \mathbf{s}(j) = \mathbf{v}^*(k)$  to obtain  $\mathbf{s}(j)$ ; and 3) gating signal generation.

1) Optimal Solution of  $\overline{\nu}(k)$  and its Feasibility: Intuitively (refer to (7)), the minimum value of (9) occurs when e(k) = 0 or

$$\bar{\mathbf{v}}(k) - \mathbf{D}^{-1}\mathbf{C}\mathbf{x}(k) + \mathbf{r}(k) \stackrel{\Delta}{=} \mathbf{v}^*(k)$$

(10)

Regardless of the pulse-width resolution b,  $\mathbf{v}^*(\mathbf{k})$  is feasible only if (see Remark 1)

$$\begin{bmatrix} 1 & \cdots & 1 \end{bmatrix} \mathbf{v}^*(k) = 0$$

(11)

To prove that  $\mathbf{v}^*(k)$  is always feasible when  $[1 \cdots 1]$  $\mathbf{r} = 0$ ,  $\mathbf{v}^*(k)$  in (10) is written as a linear combination of  $\mathbf{r}(k)$  and  $\bar{v}(k)$  using (6)–(8)

$$\mathbf{v}^{*}(k) = \mathbf{D}^{-1}\mathbf{C}\mathbf{x}(k) + \mathbf{r}(k)$$

$$= \mathbf{D}^{-1}\mathbf{C}\sum_{j=0}^{k-1} \mathbf{A}^{k-1-j}\mathbf{B}(\mathbf{r}(j) - \bar{\mathbf{v}}(j)) + \mathbf{r}(k)$$

$$= \sum_{j=0}^{k-1} d^{-1}\mathbf{c}\mathbf{a}^{k-1-j}\mathbf{b}(\mathbf{r}(j) - \bar{\mathbf{v}}(j)) + \mathbf{r}(k)$$

(12)

Because  $[1 \cdots 1] \mathbf{r} = 0$  and  $[1 \cdots 1] \mathbf{v} = 0$ , (11) is always true.

=

2) General Solution of Matching Problem: Once the optimal and feasible value v\* is obtained, the next step is to find the appropriate gating states such that the produced average phase voltage (within one input period) equals  $v^*$ . Refer to (1), the instantaneous phase voltage can be obtained by multiplying the switching state with a transition matrix  $S_c$

$$\mathbf{S} = \begin{bmatrix} S_1 \\ S_2 \\ \vdots \\ S_N \end{bmatrix} = \begin{bmatrix} (N-1)/N & -1/N & \cdots & -1/N \\ -1/N & (N-1)/N & \ddots & \vdots \\ \vdots & \ddots & \ddots & -1/N \\ -1/N & \cdots & -1/N & (N-1)/N \end{bmatrix}$$

$$\times \begin{bmatrix} s_1 \\ s_2 \\ \vdots \\ s_N \end{bmatrix} \stackrel{\Delta}{=} \mathbf{S}_c \mathbf{s}.$$

Under b-bit pulse-width resolution, 2b phase voltages (switching states) are selected within one input period and the average phase voltage must equal  $\mathbf{v}^*$  (k), i.e., from (4) and (10)

$$\bar{\mathbf{v}}(k) - \frac{1}{2^{k}} \sum_{j=0}^{2^{k}-1} \mathbf{S}_{e} \mathbf{s}(j) - \mathbf{v}^{*}(k) - \mathbf{D}^{-1} \mathbf{C} \mathbf{x}(k) + \mathbf{r}(k)$$

(13)

Where  $\mathbf{s}(\mathbf{j})$  is the instantaneous switching state and  $S_c s$  (j) the instantaneous phase voltages. To solve (13), first observe that elements in s (*j*)  $\in RN$  are either 0 or 1 to describe the ON/OFF status of the VSI. As a result, elements of the vector

(21)

$$\frac{1}{2^{b}} \sum_{j=0}^{2^{b}-1} \mathbf{s}(j) \stackrel{\Delta}{=} \Theta = \begin{bmatrix} \alpha_{1} & \alpha_{2} & \cdots & \alpha_{N} \end{bmatrix}^{T}$$

belong to the set

$${}_{b} = \left\{ 0, \frac{1}{2^{b}}, \frac{2}{2^{b}}, \frac{3}{2^{b}}, \cdots, \frac{2^{b}-1}{2^{b}}, 1 \right\}$$

Note that the *i*th element of  $\Theta$  is the duty cycle for the *i*th inverter phase leg and the finite set  $\mathbf{S}_b$  is induced by the *b*-bit pulse-width resolution within one input period. Once the vector  $\Theta$  is obtained, the gating signal can be produced accordingly. From (13) and the definition of  $\Theta$ , we can write the matching problem as

$$\mathbf{S}_{c}\boldsymbol{\Theta} = \mathbf{D}^{-1}\mathbf{C}\mathbf{x}\left(k\right) + \mathbf{r}\left(k\right)$$

(14)

Where elements of  $\Theta$  belong to  $S_b$ . The next step would be finding  $\Theta$  with elements belonging to  $S_b$ that satisfy (14).

The process is similar to the one in that derives the general solution of multiphase SVPWM. It was proved in that the circulant and symmetric matrix Sc has eigenvalues  $\xi_n$ , n = 0 - N - 1, in the form

$$\xi_n = 1 - \frac{1}{N} \sum_{m=0}^{N-1} \phi_n^m,$$

where

$$\phi_n = e^{-(2\pi n/N)j}$$

And the associated eigenvectors are

$$\mathbf{v}_n = \frac{1}{\sqrt{N}} \begin{bmatrix} 1 & \phi_n & \phi_n^2 & \cdots & \phi_n^{N-1} \end{bmatrix}^T$$

Obviously, the matrix Sc has an eigenvalues of zero and all other eigenvalues are 1. The eigenvector corresponding to the zero eigenvalues is

$$\mathbf{v}_0 = \begin{bmatrix} \frac{1}{\sqrt{N}} & \frac{1}{\sqrt{N}} & \cdots & \frac{1}{\sqrt{N}} \end{bmatrix}^T$$

. Hence, the eigenvalues decomposition of the matrix  $\mathbf{S}_c$  becomes

$$\mathbf{S}_{c} = \begin{bmatrix} \mathbf{V}_{c} \\ \mathbf{v}_{0}^{T} \end{bmatrix} \begin{bmatrix} \mathbf{I} & \mathbf{0} \\ \mathbf{0} & \mathbf{0} \end{bmatrix} \begin{bmatrix} \mathbf{V}_{c} \\ \mathbf{v}_{0}^{T} \end{bmatrix}$$

(15)

Where  $\mathbf{V}_c \in R^{(N-1) \times N}$ , whose row vectors are eigenvectors corresponding to the eigenvalues of 1. From (15), (14) becomes

$$\begin{bmatrix} \mathbf{V}_c \\ 0 \end{bmatrix} \boldsymbol{\Theta} = \begin{bmatrix} \mathbf{V}_c \\ \mathbf{v}_0^T \end{bmatrix} \mathbf{v}^* (k)$$

(16)

This leads to

$$V_c \left( \boldsymbol{\Theta} - \mathbf{v}^* \left( k \right) \right) = 0 \tag{17}$$

And

$$\mathbf{v}_0^T \mathbf{v}^* \left( k \right) = 0 \tag{18}$$

Equation (18) is always true since (11) is always satisfied. From (17), the solution  $(\Theta - \mathbf{v}^*(k))$  must lie in the right null space of the matrix  $\mathbf{V}_c$ . One can easily see that the right null space is vector  $\mathbf{v}0$  as all row vectors of  $\mathbf{V}c$  are orthogonal to  $\mathbf{v}_0$ . Therefore, the general solution of (17) (regardless of finite pulsewidth resolution) can be represented by

$$\Theta = \mathbf{v}^* \left( k \right) + \lambda \mathbf{d} \tag{19}$$

(19) Where  $\mathbf{d} = [1 \ 1 \cdots 1]^T$  and  $\lambda$  is an arbitrary real value. Because elements in  $\boldsymbol{\Theta}$  should be positive,  $\lambda$  is selected to be greater than the negative value of the smallest value in the vector  $\mathbf{v}^*(k)$ , i.e.

$$\lambda\left(k\right) \ge -\min\left(\mathbf{v}^{*}\left(k\right)\right) \tag{20}$$

Notably, elements of the right-hand-side vector in (19) are arbitrary positive values, i.e., a *b*-bit quantization is needed to find applicable duties in  $\Theta$  and is denoted as

$$\Theta\left(k\right) = q_b\left\{\mathbf{v}^*\left(k\right) + \lambda \mathbf{d}\right\}$$

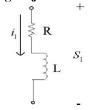

Where elements of  $q_b$  {y} are defined as the nearest value of the element in  $S_b$  to y. The block diagram of the proposed modulator is shown in Fig. 3. In the implementation,  $q_b$  {.} involves only bit truncation.

3) Gating Sequence Generation Pattern: The vector  $\boldsymbol{\Theta}$  is the corresponding duties for an *N*-phase VSI system. Once the vector  $\boldsymbol{\Theta}$  is obtained, the gating signals can be produced accordingly. As an illustrative example,

define

$$q_b \{ \mathbf{v}^* (k) + \lambda \mathbf{d} \} = [\rho_1 \quad \rho_2 \quad \cdots \quad \rho_N]^T$$

i.e., (21) becomes

$$\Theta(k) = q_b \{ \mathbf{v}^* (k) + \lambda \mathbf{d} \} = [\rho_1 \quad \rho_2 \quad \cdots \quad \rho_N]^T$$

(22)

Fig. 4 shows two examples of the gating signals for upper switches (refer to Fig. 1).

# Fig. 4. Examples of gating signals. (a) Single-sided method. (b) Central method.

# **Performance Analysis**

# A. Range of $\lambda$ and its Influence:

The value of  $\Theta$  is fixed once  $\lambda$  is selected [refer to (22)]. To have feasible duties, elements of  $\Theta$ ,  $\rho i$ , for i = 1 - -N, should be kept within the range  $0 \le \rho i \le 1$ . Therefore, the acceptable range of  $\lambda$  is limited. To see this, first define the permutation matrix  $\mathbf{P}_M$  as

$$\mathbf{P}_{M} \mathbf{v}^{*} (k) = \begin{bmatrix} \hat{v}_{1} & \hat{v}_{2} & \cdots & \hat{v}_{N} \end{bmatrix}^{T}$$

Such that  $\hat{v}_{1} \ge \hat{v}_{2} \ge \cdots \ge \hat{v}_{N}$  (23)

Therefore

$\mathbf{P}_{M} q_{b} \{ \mathbf{v}^{*} (k) + \lambda \mathbf{d} \} = \begin{bmatrix} \hat{\rho}_{1} & \hat{\rho}_{2} & \cdots & \hat{\rho}_{N} \end{bmatrix}^{T}$ (24) Where  $\hat{\rho}_{1} \geq \hat{\rho}_{2} \geq \cdots \geq \hat{\rho}_{N}$ . Then, the feasible

Where  $p_1 \ge p_2 \ge r_2 \ge p_N$ . Then, the feasible range of  $\rho i$ , for i = 1 - -N, is  $\max(\Theta) = \hat{\sigma} - \sigma \cdot [\hat{\sigma} + 1d] \le 1$

$$\max\left(\Theta\right) = \rho_1 = q_b \left\{v_1 + \lambda \mathbf{d}\right\} \le 1$$

$$\min\left(\Theta\right) = \rho_N = q_b \left\{v_N + \lambda \mathbf{d}\right\} \ge 0 \quad (25)$$

Or alternatively,  $-\hat{v}_N \leq \lambda \leq 1 - \hat{v}_1$  regardless of finite pulse width resolution, and  $-\hat{v}_N + \frac{1}{2^{b+1}} \leq \lambda \leq 1 - \hat{v}_1 - \frac{1}{2^{b+1}}$  conside ring *b*-bit pulse-width resolution.

Applying the coefficient  $\beta \in [0 \ 1]$ ,  $\lambda$  can be written as

$$\lambda = (1 - \beta) \left( -\hat{v}_N + \frac{1}{2^{b+1}} \right) + \beta \left( 1 - \hat{v}_1 - \frac{1}{2^{b+1}} \right)$$

(26)

Remark 2: Refer to Fig. 4, 2N switching number occurs within one input period. When  $\lambda$  is selected as its boundary value,  $-\hat{v}_N + \frac{1}{2^{b+1}}$  or  $1 - \hat{v}_1 - \frac{1}{2^{b+1}}$ , the switching number is reduced to 2 (N - 1) since either  $\hat{\rho}_1 = 1_{\text{or}}$

$\hat{\rho}_N = 0_{\text{occurs which implies one phase leg}}$  staying at the same level during the whole input period.

#### **B.** Minimum Total Conduction Time:

The total conduction time is defined as the sum of duties of the active gating states applied within one input period. Minimum total conduction time implies the maximum modulation index. Note that for an *N*-phase VSI system, 2*N* gating states exist and two zero switching states, s0 and s2*N* -1, correspond to the same space vector,  $\mathbf{S} = \mathbf{0}$ . Maximizing the duties of  $\mathbf{s}_0$  and  $\mathbf{s}_2N$  -1 results in minimum total conduction time.

Consider the permutated phase duty vector  $\mathbf{P}_M \boldsymbol{\Theta}$  [see (22) and (24)]. It is intuitive that the maximum duties for  $\mathbf{s}_0$  and  $\mathbf{s}_2 N - 1$  are  $1 - \hat{\rho}_1$  and

$\hat{\rho}_N$ , respectively. Therefore, the minimum total conduction time is obtained by subtracting the duty of  $\mathbf{s}_2 N - 1$  from the maximum duty among phase legs  $\hat{\rho}_1 - \hat{\rho}_N$ .

Remark 3: From remark 2, give  $\lambda = -\hat{v}_N + \frac{1}{2^{b+1}}$  or  $1 - \hat{v}_1 - \frac{1}{2^{b+1}}$ , and the modulator has minimum switching number 2 (N - 1). Therefore, the proposed gating signal generator operates at minimum total conduction time and minimum switching number point, yielding a maximum modulation index and minimum switching loss.

#### **C. Quantization Error:**

The quantization error vector  $\Delta_b$  is defined as the difference between input and output of the quantizer qb {.} which is the same as the conventional methods, i.e. (refer to Fig. 3)

$$\Delta_b = (\mathbf{v}^* + \lambda \mathbf{d}) - q_b \{ (\mathbf{v}^* + \lambda \mathbf{d}) \}$$

(27)

The concept of error analysis is extended to the MIMO system.  $\mathbf{e}$  in (7) is written as the following expression using (9) and (10) and Fig. 3:

$$\mathbf{e} (k) = \mathbf{Cx} (k) + \mathbf{D} (\mathbf{r} (k) - \bar{\mathbf{v}} (k))$$

=  $\mathbf{Cx} (k) + \mathbf{Dr} (k) - \mathbf{DS}_c q_b \{\mathbf{v}^* (k) + \lambda d\}$

=  $\mathbf{D} (\mathbf{v}^* (k) - \mathbf{S}_c q_b \{\mathbf{v}^* (k) + \lambda d\})$  (28)

Then from (27), (28) becomes

$$\begin{aligned} \mathbf{e}\left(k\right) &= \mathbf{D}\left(\mathbf{v}^{*}\left(k\right) - \mathbf{S}_{c}q_{b}\{\mathbf{v}^{*}\left(k\right) + \lambda\mathbf{d}\}\right) \\ &= \mathbf{D}\left(\mathbf{v}^{*}\left(k\right) - \mathbf{S}_{c}\left(\mathbf{v}^{*}\left(k\right) + \lambda\mathbf{d} - \boldsymbol{\Delta}_{b}\right)\right) \\ &= \mathbf{D}\left(\mathbf{v}^{*}\left(k\right) - \left(\mathbf{v}^{*}\left(k\right) - \mathbf{S}_{c}\boldsymbol{\Delta}_{b}\right)\right) \\ &= \mathbf{D}\mathbf{S}_{c}\boldsymbol{\Delta}_{b} \end{aligned}$$

Therefore, the signal e is dependent on the quantization error  $\Delta_b$ . Notably, the portion  $S_c\Delta_b$  is the influence of quantization error  $\Delta b$  on the load. Further, because the filter matrix is in diagonal form, D is a diagonal matrix, i.e., e is the scaled quantization error that appears on the load windings and is minimized by the proposed modulator.

#### Matlab Design of Case Study

Simulation that compares the influence of filter matrix is done under the five-phase setting. MATLAB is used as a simulation platform. Five-phase sinusoidal references with large/small modulation indices are applied to verify the compensating ability of the proposed switching strategy.

The modulator with first- and second-order weighting filters is compared with the conventional SVPWM

under the digital implementation settings. The weighting filters are the first- and second-order integrator systems, z/(z - 1) and z 2/(z - 2z + 1). We denote the one having no feedback loop as SVPWM. The system state-space matrices for the first- and second-order filter matrices are a = b = c = d = 1(denoted as PWM\_1st). Referring to Fig. 3, the implementation block diagram is shown in Fig. 5. Notably, no multipliers are needed in the implementation. Because the coefficients of filters are either 1 or 2, only adders and shifters are needed to implement weighting filter.

## **Simulation Results**

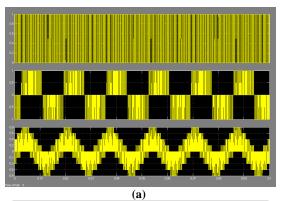

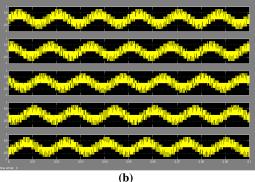

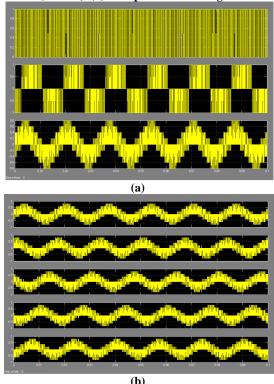

A five-phase sinusoidal reference input with normalized amplitude 0.51 and frequency 60 Hz is applied. The carrier frequency is 3 kHz and the pulsewidth resolution is 8, yielding a clock rate of  $2^8 \times 3k =$ 768kHz. Figs. 7(a)-8(a) show one of the leg voltages, line-to-line voltages, and phase voltages for the aforementioned PWMs. The five-phase voltages produced on the load are also shown in Figs. 7(b)-8(b) to verify the correctness of the gating signals. To have a precise comparison, Tables I lists the switching number and the harmonic distortion for modulation indices 0.51. It is seen that with the shaping filter that relocates the noise in the higher frequency band, the harmonic distortion of PWM\_1st is reduced within [0 500] Hz compared to that of SVPWM, especially for small modulation indexThe harmonic distortion within [0 5 k] Hz for these systems is comparable yielding approximately the same level of error power which is induced by finite pulse-width resolution. Therefore, with the shaping filter, components of error tend to be distributed over high-frequency band.

#### TABLE I- HARMONIC DISTORTION AND SWITCHING NUMBER FOR 8-BIT PULSE-WIDTH RESOLUTION (WITH INPUT AMPLITUDE 0.51)

| Input amplitude: 0.51                          | SVPWM  | $PWM\_l^{st}$ |

|------------------------------------------------|--------|---------------|

| Harmonics distortion<br>within [0 500] Hz (%)  | 0.439  | 0.244         |

| Harmonics distortion<br>within [0 5000] Hz (%) | 43.072 | 43.150        |

| Switching number<br>( per second)              | 24k    | 24k           |

Fig. 7. Simulation results of SVPWM. (a) Leg voltage (top), line-to line voltage (middle), and phase voltage (bottom). (b) Five-phase load voltages.

Fig. 8. Simulation results of PWM\_1st. (a) Leg voltage (top), line-to-line voltage (middle), and phase voltage (bottom). (b) Five-phase load voltages.

### Conclusion

In the present paper a filtered space-vector pulse-width modulation (SVPWM) considering finite pulse-width resolution has been proposed to produce a switching sequence with reduced baseband harmonics for multiphase voltage source inverters (VSI). This is achieved by incorporating a pseudo feedback loop regarding weighted voltage difference between desired and produced phase voltages.

The simulation results state that SVPWM is sensitive to the pulse-width resolution. By applying the feedback loop with weighting filter, the harmonic distortion is reduced compared with conventional SVPWM.Further more the results indicate that the proposed model is capable of providing satisfactory performance at low frequencies particularly.

#### References

- [1] H. John and A. G. Duncan, "The use of harmonic distortion to increase the output voltage of a three-phase PWM inverter," IEEE Trans. Ind. Appl., vol. IA-20, no. 5, pp. 1224–1228, Sep./Oct. 1984.

- [2] Z. Keliang and W. Danwei, "Relationship between space-vector modulation and threephase carrier-based PWM: A comprehensive analysis," IEEE Trans. Ind. Electron., vol. 49, no. 1, pp. 186–196, Feb. 2002.

- [3] O. Lopez, J. Alvarze, D. G. Jesus, and F. D. Freijedo, "Multilevel multiphase space vector PWM algorithm with switching state redundancy," IEEE Trans. Ind. Electron., vol. 56, no. 3, pp. 792–804, Mar. 2009.

- [4] Y. H. Liu, C. L. Chen, and R. J. Tu, "A novel space-vector current regulation scheme for a field-oriented-controlled induction motor drive," IEEE Trans. Ind. Electron., vol. 45, no. 5, pp. 730–737, Oct. 1998.

- [5] D. W. Chung, J. S. Kim, and S. K. Sul, "Unified voltage modulation technique for real-time three-phase power conversion," IEEE Trans. Ind. Appl., vol. 34, no. 2, pp. 374–380, Mar./Apr. 1998.

- [6] D.G.Holmes, "The significance of zero space vector placement for carrier based PWM schemes," IEEE Trans. Ind. Appl., vol. 32, no. 5, pp. 1122–1129, Sep./Oct. 1996.

- [7] A. Trzynadlowski and S. Legowski, "Minimum-loss vector PWM strategy for three-phase inverter," IEEE Trans. Power Electron., vol. 9, no. 1, pp. 26–34, Jan. 1994.

- [8] A.M. Hava, R. Kerkman, and T. A. Lipo, "Carrier-based PWM-VSI over modulation strategies: Analysis, comparison, and design," IEEE Trans. Power Electron., vol. 13, no. 4, pp. 674–689, Jul. 1998.

- [9] A. Trzynadlowski, R. L. Kirlin, and S. Legowski, "Space vector PWM technique with minimum switching losses and variable pulse rate," IEEE Trans. Ind. Electron., vol. 44, no. 2, pp. 173–181, Apr. 1997.

- [10]S. Williamson and S. Smith, "Pulsating torque and losses in multiphase induction machines," IEEE Trans. Ind. Appl., vol. 39, no. 4, pp. 986–993, Jul./Aug. 2003.

- [11]S. Dwari and L. Parsa, "An optimal control technique for multiphase PM machines under open-circuit fault," IEEE Trans. Ind. Electron., vol. 55, no. 4, pp. 1988–1995, May 2008.

- [12]A. Iqbal and S. Moinuddim, "Comprehensive relationship between carrier based PWM and space vector PWM in a five-phase VSI," IEEE Trans. Power Electron., vol. 24, no. 10, pp. 2379–2390, Oct. 2009.